Filter News

Area of Research

News Type

News Topics

- (-) Bioenergy (4)

- (-) Biomedical (2)

- (-) Microscopy (2)

- (-) Physics (4)

- (-) Summit (2)

- 3-D Printing/Advanced Manufacturing (10)

- Advanced Reactors (2)

- Artificial Intelligence (2)

- Big Data (2)

- Clean Water (1)

- Computer Science (7)

- Coronavirus (6)

- Cybersecurity (2)

- Energy Storage (7)

- Environment (5)

- Exascale Computing (1)

- Grid (3)

- Machine Learning (2)

- Materials Science (10)

- Mathematics (2)

- Nanotechnology (2)

- Neutron Science (3)

- Nuclear Energy (4)

- Quantum Science (1)

- Security (1)

- Sustainable Energy (3)

- Transformational Challenge Reactor (2)

- Transportation (5)

Media Contacts

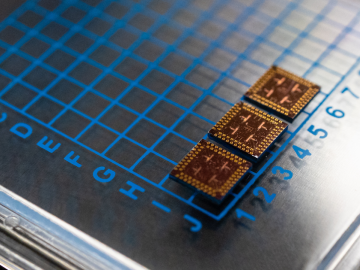

Scientists at have experimentally demonstrated a novel cryogenic, or low temperature, memory cell circuit design based on coupled arrays of Josephson junctions, a technology that may be faster and more energy efficient than existing memory devices.